更多“ADC0809引脚OE是()信号,高电平有效。”相关的问题

更多“ADC0809引脚OE是()信号,高电平有效。”相关的问题

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

假设81C55的TIMERIN引脚输入的脉冲频率为1MHz,请编写出在81C55的 引脚上输出周期为10ms的方波的程序。

引脚上输出周期为10ms的方波的程序。

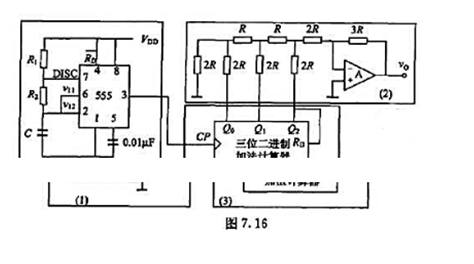

(1)说明虚框(1)、(2)部分各构成什么功能电路?

(2)虚框(3)构成几进制计数器?

(3)对应CP西出Vo波形,并标出电压值.

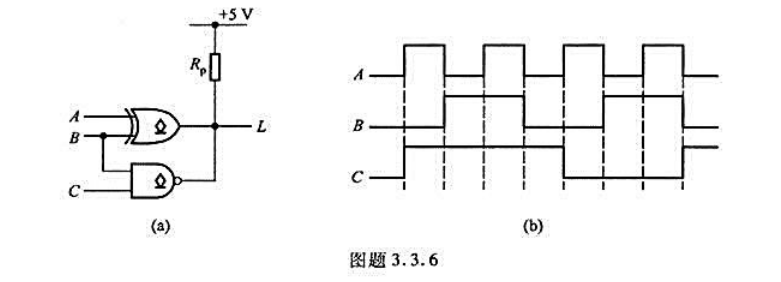

由OD异或门和OD与非门构成的电路及输入电压波形如图题3.3.6所示。

(1) 试写出输出与输入的逻辑关系式,画出输出电压波形。

(2) 已知输出低电平VOL(max)=0.33V时的最大输出电流IOL(max)=4mA,输出高电平VOH(min)=4.4V时的漏电流lOZ=5μA,计算Rp(min)和Rp(max)。