更多“设计一个数据判断电路,当4位二进制数据DCBA的数值在001…”相关的问题

更多“设计一个数据判断电路,当4位二进制数据DCBA的数值在001…”相关的问题

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

问题描述;设S是正整数集合.S是一个无和集,当且仅当 蕴含

蕴含 .对于任意正整数k,如果可将{1.2,...,k}划分为n个无和子集

.对于任意正整数k,如果可将{1.2,...,k}划分为n个无和子集 ,则称正整数k是n可分的.记F(n)=max{k|k是n可分的}.试设计一个算法,对任意给定的n,计算F(n)的值.

,则称正整数k是n可分的.记F(n)=max{k|k是n可分的}.试设计一个算法,对任意给定的n,计算F(n)的值.

算法设计:对任意给定的n,计算F(n)的值.

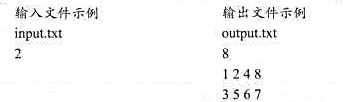

数据输入:由文件input.txt给出输入数据.第I行有1个正整数n.

结果输出:将计算的F(n)的值以及{1,2,F(n)}的一个n划分输出到文件output.txt.文件的第1行是F(n)的值.接下来的n行,每行是一个无和子集Si.

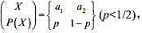

设信源 其失真度为汉明失真度,试问当允许平均失真度D=p/2时,每一信源符号平均最少需要由几个二进制数据符号表示?

其失真度为汉明失真度,试问当允许平均失真度D=p/2时,每一信源符号平均最少需要由几个二进制数据符号表示?

问题描述:设p是奇素数,1≤x≤p-1,如果存在一个整数y(1≤y≤p-1),使得x=y2(modp),则称y是x的模p平方根.例如,63是55的模103平方根.试设计一个求整数x的模p平方根的拉斯维加斯算法.算法的计算时间应为logp的多项式.

算法设计:设计一个拉斯维加斯算法,对于给定的奇素数p和整数x,计算x的模p平方根.

数据输入:由文件input.txt给出输入数据.第1行有2个正整数p和x.

结果输出:将计算的x的模p平方根输出到文件output.txt.当不存在x的模p平方根时,输出0.

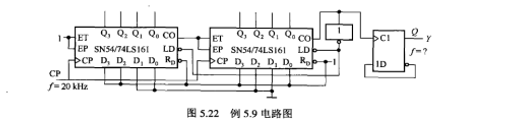

由两片SN54/74LS161(同步4位二进制计数器)组成的同步计数器如图5.22所示.

1)试分析其分频比(即Y与CP之频比),当CP的频率为20kHz时,Y的频率为多少?

2)试用2片SN54/74LS161组成模为91的计数器,要求两片间用级联法,并工作可靠.