更多“电压测量档位,量程越大,则与输入端并联的电阻越()。”相关的问题

更多“电压测量档位,量程越大,则与输入端并联的电阻越()。”相关的问题

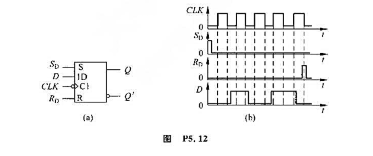

在图P5.12(a)下降触发D触发器中,已知时钟脉冲CLK、输入端D、异步置位输入端RD和异步复位输入端RD的电压波形如图P5.12(b)中所示,试画出输出端Q对应的电压波形。

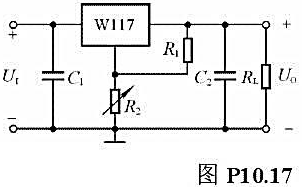

(1)输出电压的调节范围;(2)输入电压允许的范围.

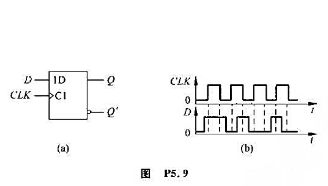

画出图P5.9(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CIK和输入端D的电压波形如图P5.9(b)所示。设触发器的初始状态为Q-0。

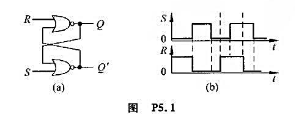

画出图P5.1(a)中SR锁存器Q和Q'端的电压波形。输入端S和R的电压波形如图P5.1(b)所示。

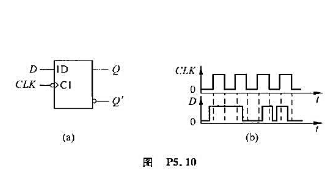

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。

试证明图7.7.7(d)所示单端输入,单端输出差分电路的差模电压放大倍数和输入电阻分别为

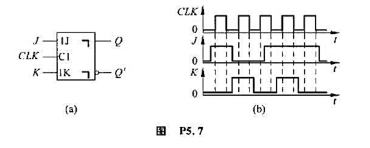

画出图P5.7(a)中脉冲触发JK触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入J、K的电压波形如图P5.7(b)所示。设触发器的初始状态为Q=0。

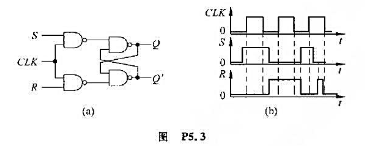

画出图P5.3(a)中电平触发SR触发器Q和Q'端的电压波形。时钟脉冲CLK及输入S、R的电压波形如图P5.3(b)所示。设触发器的初始状态为Q=0。

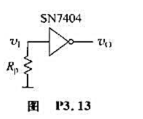

在图P3.13电路中,试求Rp为51Ω、1.5kΩ、100kΩ和∞(输入端悬空)时υ1和υ0的数值。已知电源电压Vcc=5V,反相器SN7404的电路结构图如图3.4.1,它的电压传输特性如图3.4.3所示。

画出图P5.15(a)中两个T触发器FF1和FF2的输出端Q1和Q2的电压波形。时钟脉冲CLK和输入端T的电压波形如图P5.15(b)所示。设触发器的初始状态均为Q=0。